| Название | : | Behaviour of Master Slave D Flip Flop |

| Продолжительность | : | 11.48 |

| Дата публикации | : | |

| Просмотров | : | 651 rb |

|

|

What is the difference between Qm and Qp ? Comment from : Rahul Srinivasan |

|

|

Lectures are 8 year old but still these lectures are very much helpful to all the engineers specially to EC, EE, IN And CS students😊 Comment from : Prinsu Singh |

|

|

Thanks! For a positive-edge triggered flip-flop, just invert the clock signal (So much for the obvious ;) ) Comment from : Zev Farkas |

|

|

Very well explained ❤️ Comment from : Arunjith R |

|

|

great, I think the for getting positive edge triggered flip flop, the clocks can be reversed Not gated clock for master flip flop and direct input for slave flip flop Comment from : Chandra Samsung |

|

|

It would be nice if you gave explanation of certain facts as well as cause-reason connections What I mean, is sometimes it’s not clear why truth tables are written as they are Eg when clock is active it means it orders data to be memorised, and when inactive, any data can pass through I hope I have explained my point well Thank you again for your work! ❤️ Comment from : Augusta Averence |

|

|

Very easy teaching also from basic Comment from : Aniket Rajapure |

|

|

Will all time slave conf will be same as of negative edge trigg Comment from : Jayesh |

|

|

What a great knowledge, I pray to be like you Sir in Electronics WorldbrThank you very much and Remain Blessed! Comment from : Omene Chris |

|

|

Thank you soo much sir it was a saver Comment from : Vajeela Begam |

|

|

Main Purpose of Master-slave flip is to remove glitches Comment from : Tech BitoCracy |

|

|

you used leve triggering for the master slave flip flop and edge triggering for the simple flip flop right? Comment from : Informative Videos |

|

|

why master D flip flop is behaving like level sensitive it should not change when clock is high ? Comment from : Dhiraj Ameta |

|

|

I can not understand what is the Qp and Qn Can anyone tell me? Comment from : Cemile Ceylan |

|

|

great Comment from : Bijoy roy chowdhury prinon |

|

|

very much helpful and the fact that the videos are of maximum 15 minutes makes it very much learning I used to fear from Digital Logic Design ,n after watching your video i am able to understand the concept very well Comment from : Shreyans Jain |

|

|

You are saving me from backlog 😂 Comment from : Shaiq hussain ELE 5029 |

|

|

I love when he says if we have any problems to comment below Comment from : Shirin Nurlyyeva |

|

|

Difference between you and my prof is you can understand it simply solving an example Comment from : Anar Nasirov |

|

|

thank you so much sir! this video totally save me!! Comment from : az |

|

|

Really videos are the best sir ,I am doing verliog and system verilog course sir, I needed the basic of this digital ones your videos are very worth and very beneficial sir I have one doubt sir is glitches and race around condition are same sir?? Comment from : shrungin vk |

|

|

It has been most amazing lecture I have seen on master slave flip flop Comment from : Dhairya Oza |

|

|

Thank you I think is not flip-flop its latch Comment from : HUSSAIN ALMANSORY |

|

|

your explanation is very clear and on point, thank you so much for your hard work Comment from : Hind Baageel |

|

|

Sir in your previous D-FF video you said that it works like a level triggered FF, but here from the graph we see that it is working as -ve edge trigg FFcan you explain this Comment from : Arko Bhattacharya |

|

|

very very very thankyou, all are very helpful for me 🧡🧡br love from Bangladesh 💚 Comment from : Md Khairul Islam |

|

|

great lecture sir Comment from : Rakshit Pandey |

|

|

sir , is chracteristic table same for master slave as simple d flip flop ? Comment from : Chillpink wanderer |

|

|

Such a nice and clear explanation Comment from : Shivani Singh |

|

|

Great explanation:), but for me, you speak fast hahaha I played it at 075x so I can follow Comment from : THE ARITHMOS |

|

|

아주 좋아요 ㅎ Comment from : 꿀토실 |

|

|

1hour before the exam Comment from : Belal Essabri |

|

|

Good Video lecture sir, I have a doubt in your video of master slave flip flip- Let see in the Qm output- you showed two glitches, the second glitches is dropped down without complete one cycle of clock is it write? it confused about to me timing from br4:06 to 5:15 Comment from : Manoj Prabhakaran |

|

|

why are there no glitches in Qp? Comment from : BREATHE MUSIC |

|

|

Please change the intro music its a old music Please Comment from : madushan prathap |

|

|

😘🥰❤💗🥳🤘 for all digital electronics video u have done I love this course because hard topic are cleared In easy way 😘 Comment from : Chandan R |

|

|

Really helpful Lectures Thankyou so much Comment from : Stuti Rajeev |

|

|

Thopu bro nuvvu Comment from : pavan ambala |

|

|

you don't explain graphs well Comment from : Abhishek Chaurasia |

|

|

i have a doubt sirji, You haven't considered delay in any of the Waveform, but in gate Questions answers dely is considered by default, big doubt😭😭 Comment from : Pankaj Singh Rawat |

|

|

Why no glidges formed in negative edge triggered? While Qm has glidges Comment from : hari haran |

|

|

Thank you so much for this video 😊 Comment from : Hashi_Pur |

|

|

sir don't say thanks for watching WE SHOULD THANK YOU FOR THE LECTURES YOU ARE INSPIRATION FOR MANY THANKS FOR THE AMAZING LECTURE SERIES Comment from : Satyam Kumar Singh |

|

|

How old are you sir? Comment from : Nitish Sharma |

|

|

I want to join hands with neso academy Comment from : Prasanna Kumar |

|

|

really appreciable work thanks man Comment from : naman kukreja |

|

|

A crores of thanks from me🙏🙏🙏🙏🙏🙏🙏🙏 Comment from : akash kadambi |

|

|

this is D Latch no D flip flop as in the D flip flop the signal can you change once during a positive till negative edge triger Comment from : Rony |

|

|

No doubt sirbrAll the doubts are at one side and your explanation is at another side 👍👍👍😊😊😊 Comment from : Shubham Desai |

|

|

Very nice sir Comment from : Angel Manisha |

|

|

PLEASE MAKE VIDEOS ON DIGITAL LOGIC FAMILIES (TTL, ECL, CMOS etc) and ADC and DAC conversions

brYour lectures are great

brThank you so much for them Comment from : Pranav Shukla |

|

|

whether the clock is edge triggered or level triggered? Comment from : Pon radhakrishnan |

|

|

Your explanation is fantastic,you can upload more videos Comment from : niki Konuri |

|

|

Very Nice! Keep it up man Comment from : Hizbi |

|

|

When we consider edge triggered flip flop, why don't we consider as master slave D-Flip Flop? Comment from : Christian Polignano |

|

|

Why does D flip flop correspond to positive edges? Comment from : Yong Hui Liew |

|

|

Thankyou sir Comment from : B Lakshmi Priya |

|

|

Why the glitches are not good Comment from : Arashpardeep Singh |

|

|

you did not mention the use of preset and clear in any of your lectures Comment from : Sriparno |

|

|

Thanks Sir, its very clear Comment from : HEDI GUESMI |

|

|

It was a very good lecture Thanks a lot brbrQm: (high)level triggered o/p of master ffbrQs: (low) level triggered o/p of slave Ff for input Qm brQp,Qs: edge triggered waveform of data input signal Comment from : murali hanumanth |

|

|

You Teach In More Informative Way Than My Teacher Great Man, I Have Paper Tomorrow, I Think It Won't Be Difficult For Me After Watching This Again Thanks Man Comment from : Wait_Wait Top 3 |

|

|

cant understand properly this video /// Comment from : Akshyah dhiman |

|

|

What would happen if the D input shifted slightly to left side so that it is high at the place of negative edge?? Comment from : Vysakh K U |

|

|

I had been struggling about this topic for a long time, and did not understand anything But now EVERYTHİNG IS CLEAR THANKS TO YOUR VIDEOS Thank you so much sir, may God bless you Comment from : Fzehra |

|

|

Can we take any random waveform for 'D' signal Comment from : Mandara BC |

|

|

You're the best man :) Comment from : Ghazal Tajik |

|

|

WHY YOU DRAW GLITCHES IN QM? Comment from : MrShortReels |

|

|

So much hardworking done by you for explaining and for making diagrambrkeep doing Comment from : Dhruv Chavda |

|

|

Arrow will not be there if its edge triggering? Comment from : Nishit Mangal |

|

|

5:10 are you sure that Qm will remain high till the middle of 5 and not till the next high pulse ? Comment from : Tuhin Mitra |

|

|

no feed back? for master slave operation on d flip flop? or you forgot? Comment from : N K |

|

|

Qm cannot go high until the next clock edge Master is behaving as level triggered latch and not flip flop as you are saying Can you make correction in this video? Comment from : Yasaswy Jandhyala |

|

|

Awesome Comment from : Rafat Ashraf |

|

|

vera level!!!! Comment from : arjun |

|

|

Paragliding se jada fun to in lectures me hai 😍 Comment from : Pratyush Tiwari |

|

|

Qm is level triggered so it should be a latch right?Why is it called a flip flop ?Someone please explain Comment from : Akhila |

|

|

Sir, why do we consider both flip flops as level triggered? Are those D latches? Comment from : Sanjay Nanda |

|

|

Sir i have just come out from a boring lecture of digital electronics I don't want to sit there and waste my time and i am here watching your lectures Thank you so much sir Comment from : sowmya s |

|

|

Sir, whether d ff edge triggered or level Why the d ff used in ms ff is level triggerd when d ff is edge triggered Comment from : Arpit Goel |

|

|

Thanku so much Comment from : Thanuja Kollipara |

|

|

Super lecture Comment from : Logesh Waran |

|

|

YOU RE THE ONE THAT I LOVE OOH OOH OOH YEAH Comment from : Vasilis Christoulas |

|

Flip Flop In Digital Electronics | Types Of Flip Flops Circuits | Flip Flop In Digital Logic design РѕС‚ : Pywix Classes Download Full Episodes | The Most Watched videos of all time |

|

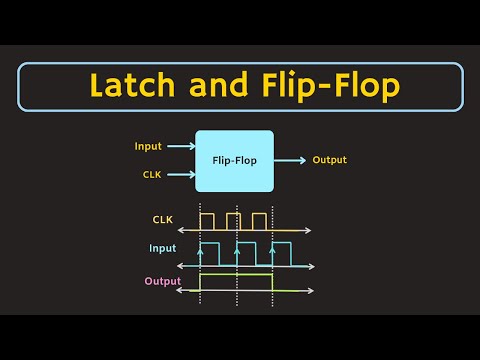

Latch and Flip-Flop Explained | Difference between the Latch and Flip-Flop РѕС‚ : ALL ABOUT ELECTRONICS Download Full Episodes | The Most Watched videos of all time |

|

Flip Flop in Digital Electronics in Hindi|SR Flip Flop|Zeenat Hasan Academy РѕС‚ : Zeenat Hasan Academy Download Full Episodes | The Most Watched videos of all time |

|

شرح قلاب SR الاول | SR Flip-Flop | Latches and Flip-flops | Set Reset Flip-flops РѕС‚ : منتظر نعيم Muntadher Naeem Download Full Episodes | The Most Watched videos of all time |

|

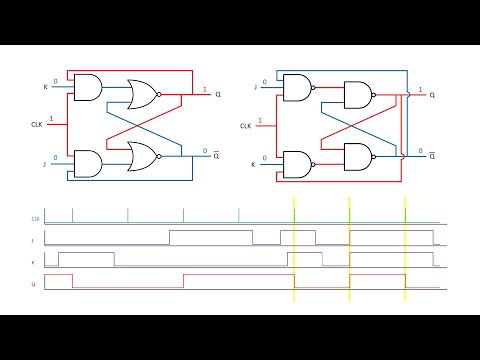

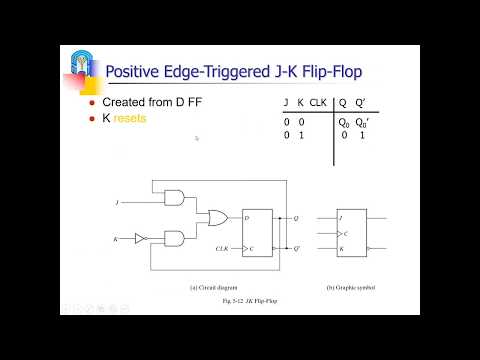

Latches and Flip-Flops 6 - The JK Flip Flop РѕС‚ : Computer Science Download Full Episodes | The Most Watched videos of all time |

|

الـ Flip Flop (القلابات) IC 4013 (ابسط شرح) РѕС‚ : Nouryas Tech Download Full Episodes | The Most Watched videos of all time |

|

Logic Circuit Design #19 Sequential circuit Latch (SR u0026 D)u0026 Flip flop (D, T, JK) دوائر التسلسل РѕС‚ : Hashim EduTech Download Full Episodes | The Most Watched videos of all time |

|

شرح Latches u0026 Flip-Flop (Digital Logic Design) الجزء 1 РѕС‚ : Haitham Alhazmy Download Full Episodes | The Most Watched videos of all time |

|

SR Flip Flop شرح РѕС‚ : TAHA1001 Download Full Episodes | The Most Watched videos of all time |

|

Introduction to T Flip Flop | Circuit, Working, Truth Table, Characteristics u0026 Excitation Table РѕС‚ : Gate Smashers Download Full Episodes | The Most Watched videos of all time |