| –ù–∞–∑–≤–∞–Ω–∏–µ | : | ZYNQ for beginners: programming and connecting the PS and PL | Part 1 |

| –ü—Ä–æ–¥–æ–ª–∂–∏—Ç–µ–ª—å–Ω–æ—Å—Ç—å | : | 22.55 |

| –î–∞—Ç–∞ –ø—É–±–ª–∏–∫–∞—Ü–∏–∏ | : | |

| –ü—Ä–æ—Å–º–æ—Ç—Ä–æ–≤ | : | 83¬Ýrb |

|

|

Great work Dom, a nice beginner tutorial Comment from : CHY |

|

|

Thank you so much for this video as it really stabilized my shaky basics Comment from : Isa Muhammad Hassan |

|

|

Exactly what I'm looking for You da man! Comment from : eigenfield |

|

|

love yr style Comment from : Pavel K |

|

|

Best tutorial Comment from : Ibn Smart |

|

|

Thank you very much

brI have followed both videos exactly as explained and changed the xdc file of ZedBoard and it's working perfectly Comment from : Chinmaya Panda |

|

|

Wow!!! Thanks! Comment from : Nikolay Kostishen |

|

|

Hello!! What should we do if there are 2 outputs? Comment from : Akshay |

|

|

Sorry I just can’t get over the fact that a NAND gate should be less transistors than an AND gate Comment from : Philip Hubbe |

|

|

Thanks for the nice video and explanation I have a problem generating bitstream, it says ERROR: [DRC NSTD-1] Unspecified I/O Standard: 3 out of 133 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value I searched some sources but could not fix it Could you help ? Comment from : Mangal Kothari |

|

|

Excellent video, could you do tutorials using a Zedboard and Vivado from 0? Comment from : Isaac Zambrano |

|

|

great stuff, good explanation Comment from : MiladM |

|

|

How you can use the RTL instantly at 10:58? There have no such option for me in Vivado 20151 or it only available for Vivado 2019br? Comment from : Andrew Lau |

|

|

Hii! Great tutorial i wanted some help in my project how can I contact you? Comment from : Mitesh V b |

|

|

In our design, axi i2c ip is continuously generating interrupts as soon as we load pl file Any suggestions Comment from : Divya Saravanan |

|

|

Thank you for great video and clear explanation üôè Comment from : Dan Shazar |

|

|

Thanks for the tutorial! Should it also work when i use the latest vitis version? i dont get it managed that it works Comment from : max maxx |

|

|

Very helpful ,thank u Comment from : Cagakan Odabas |

|

|

Finally, someone is explaining this connection, well done!!! Could you please tell me why the option "add module to block design" is greyed out in my program? Comment from : checksum1990 |

|

|

Hi dom, will you do more tutorials on the zynq fpga? Comment from : stage6 |

|

|

@9:03 you should not use RGB LEDs with 100 driven output, they should be at 50 PWM duty cycle max Below that section (as seen in video) was the standard LEDs for Arty-Z7 that are safe to drive 100, thanks for video this answered many questions I had Comment from : D M |

|

|

great thx Comment from : V-Codes |

|

|

Quite explanatory, thanks for that but please don't say bla bla bla :) Comment from : Ismail Palit |

|

|

Thank you for the video, very useful for beginners Can you upload a video on how to write data into DDR memory using RTL data from PL Comment from : Gokul Vishnu |

|

|

could you explain how to greate a board file snd how to defind MIO? Thanks Comment from : Wenyan Wang |

|

|

sir how to run the python on zinc and how to build own fpga for runinng python Comment from : SAGAR H M |

|

|

Hi, Thank you for the video DombrI wanted to know that what max Speed of IO-PIN of Micro-Zed Board with 7020? brI cannot find this information into the datasheet Can you please help me out here Comment from : Azmat ali |

|

|

Please make tutorials on the vivado software for ZC706 board Comment from : Dipika Sahoo |

|

|

Thank you! Useful videos! Comment from : Dvuong Do |

|

|

VHDL is not case sensitive, but I adhere to writing code like it were I don't know if Viviado or Verilog are case sensitive If someone would comment on this, I'd be grateful Thanks! Comment from : Richard Vasquez |

|

|

Very good explanation Thanks my friend :) Comment from : EE_TECH_CHANNEL |

|

|

Thank you, great friendly tutorial But can't we just run the NOT and the AND on the FPGA ? To avoid doing the C code on SDK?brWhat is the purpose of the processor in this FPGA? Will it not introduce delays if we gonna make a real time system ? Thank you Comment from : Muri Muri |

|

|

Many thank for your useful video I have been looking a while for a video that has both PL and PS code I hope we could see more videos like this in the future Comment from : Adnan Ghaderi |

|

|

Audio quality was fine Comment from : Tahir R |

|

|

This is an awesome video, thanks Comment from : Zain Ahmed |

|

|

Wow! Amazing I was looking for this kinda tutorial please make it more for us Comment from : M U B A S H E E R |

|

|

This is the same as transferring data from ps to pl? Comment from : Alexandros III |

|

|

Thank you very much, This is exactly what I´ve been looking for Comment from : Preon Tech |

|

|

I assume the "ZYNQ" thing is the PS, right? But usually isn't there multiple CPUs (maybe corext A53, cortex R5 for example ) in the PS and how does the "ZYNQ" know which one to use to do the "NOT" operation? Comment from : Andrew |

|

|

Many thanks for your great videos brbrI got 3 errors after Launching the Runs at "Generate bit stream"brBtw your launch box is 2 jobs mine is 4 jobs, nevertheless I redid it again like yours and still get errors, I couldn't find a solution, can you help me out here?brbr1- [DRC UTLZ-1] Resource utilization: BIBUF over-utilized in Top Level Design (This design requires more BIBUF cells than are available in the target device This design requires 260 of such cell types but only 130 compatible sites are available in the target device Please analyze your synthesis results and constraints to ensure the design is mapped to Xilinx primitives as expected If so, please consider targeting a larger device)

brbr

br2- [DRC UTLZ-1] Resource utilization: PS7 over-utilized in Top Level Design (This design requires more PS7 cells than are available in the target device This design requires 2 of such cell types but only 1 compatible site is available in the target device Please analyze your synthesis results and constraints to ensure the design is mapped to Xilinx primitives as expected If so, please consider targeting a larger device)

brbr3- [Vivado_Tcl 4-23] Error(s) found during DRC Placer not run

brbrMany thanks for your time :-) Comment from : Omar Moussa |

|

|

Good One! Comment from : shreyas borse |

|

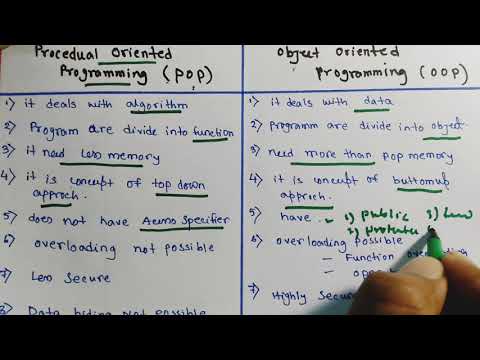

Procedure Oriented Programming and Object Oriented Programming - Java Programming Tutorial –Ý—ï–°‚Äö : Ekeeda Download Full Episodes | The Most Watched videos of all time |

|

Bao gi·ªù c√≥ th·ªÉ r√∫t ƒë∆∞·ª£c kin v·ªÅ v√≠- achi ki·∫øm ti·ªÅn online –Ý—ï–°‚Äö : Achi ki·∫øm ti·ªÅn online Download Full Episodes | The Most Watched videos of all time |

|

Zynq 7020 (Z-turn) –∏ Spartan-6: –ø–µ—Ä–≤—ã–µ –æ–ø—ã—Ç—ã –Ý—ï–°‚Äö : Fagear Download Full Episodes | The Most Watched videos of all time |

|

How To Fix PS4 Not Connecting To The Internet | PS4 Not Connecting To The WiFi Fix –Ý—ï–°‚Äö : TechHQ Download Full Episodes | The Most Watched videos of all time |

|

How To Fix PS5 Not Connecting To The WiFi | PS5 Not Connecting To The Internet –Ý—ï–°‚Äö : TechHQ Download Full Episodes | The Most Watched videos of all time |

|

Knapsack Problem using Dynamic Programming Part I | Dynamic Programming | Lec 65 | DAA –Ý—ï–°‚Äö : CSE Guru Download Full Episodes | The Most Watched videos of all time |

|

Difference between Procedural oriented programming and object oriented programming –Ý—ï–°‚Äö : Institute Academy Download Full Episodes | The Most Watched videos of all time |

|

for loop in C programming language | Malayalam C programming Language –Ý—ï–°‚Äö : SJTutorialsLive Download Full Episodes | The Most Watched videos of all time |

|

AVR Programming 0.1 - Install Eclipse IDE for AVR Programming –Ý—ï–°‚Äö : DPEE LAB Download Full Episodes | The Most Watched videos of all time |

|

Procedure Oriented vs Object-oriented Programming | Programming Languages 2020 | Edureka –Ý—ï–°‚Äö : edureka! Download Full Episodes | The Most Watched videos of all time |