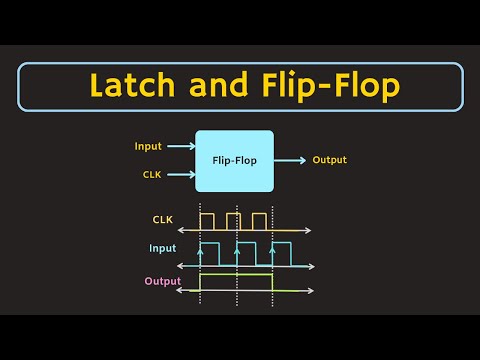

| –ù–∞–∑–≤–∞–Ω–∏–µ | : | Difference between Latch and Flip Flop |

| –ü—Ä–æ–¥–æ–ª–∂–∏—Ç–µ–ª—å–Ω–æ—Å—Ç—å | : | 5.33 |

| –î–∞—Ç–∞ –ø—É–±–ª–∏–∫–∞—Ü–∏–∏ | : | |

| –ü—Ä–æ—Å–º–æ—Ç—Ä–æ–≤ | : | 1,6¬Ýjt |

|

|

I can't understand why none of you use a simulator instead of rambling around Comment from : Birdy Jr |

|

|

good video Comment from : kartik |

|

|

hi Comment from : kartik |

|

|

I came for a Sandal Comment from : User Unknown |

|

|

I dont get it Comment from : عبد الرحمن موني |

|

|

Very good presentation H/w option B Comment from : Benard Onchieku |

|

|

Thanks Comment from : Barış İlgen |

|

|

Thank you sir Comment from : 21UEC136 Ashutosh Kumar |

|

|

nesco academy"s other subjects teacher is far better than thisi think nesco should alter the teaching skill of this subject teacherbrthis type of teaching skill dosn"t match nesco level!!!!! Comment from : Kartikey Srivastava |

|

|

7 years phle ka hai but agr thik saaf saaf likh ho to ss se kaam chl jayeit is irritating ki mai yha sirf ss lekr nhi pdh skti Comment from : Kashish Gupta |

|

|

Thank you very much sirü•≥ü•≥ü•≥ü•≥ Comment from : grƒÅ√±Ds√ñn_√∏f_pH√Æx√Øs |

|

|

Thank you Comment from : Hello World |

|

|

What would happen if we were to use NOR gates for the S and R part (gates drawn in yellow) instead of NAND gates? Comment from : Yung Banz |

|

|

The latch or ff u used isn't correct i guess Q and Q compliment position will be interchanged Comment from : Amandeep Saha |

|

|

Thnks for your guidance May ALLAH bless you Comment from : Khadija Asif |

|

|

Anyone from Nepal? Comment from : Bhaskar Thakulla |

|

|

Sir, brWhich reference book you used for this topic Tell me because in some books there are different circuit of latch and it's explanation Comment from : Amit Garg |

|

|

What is the difference between latch and flip flop?brWhen we use level triggering in the given circuit it will act as a latch, while if we use edge triggering by using a clock pulse to the circuit it will function as a flip flopbrThe latch is functional only when the signal is enabled, while the flip flop function when there is a transition b/w high to low or low to high in the clock pulse signal Comment from : Tech BitoCracy |

|

|

ü§üü§üü§üüî•üî•üî• aage badte raho Comment from : Srikanta Banerjee |

|

|

Very nice lecture Comment from : Pritha Majumder |

|

|

Thank you for posting ! Comment from : AGS-TECH Inc - Custom Manufacturing |

|

|

Wow you wrecked my university teacher in 5 minutes 32 seconds Thank you so much, i finally learned this Comment from : SM |

|

|

best channel on yt Comment from : ◊ì◊Ý◊ô◊ê◊ú |

|

|

S star is equal to S and Enable complement isn't it, it is a nand gate, it will be and and not or Comment from : Shailendra Shinde |

|

|

Someone is calling you 2:32 üòÖüòÖ Comment from : Smit Bhagat |

|

|

Thank you soo much sir , very clear explanation Comment from : SMSesha Reddy |

|

|

We are using the NAND gate but the eq you write for Q* and for S*is the eq for NOR gate brPlz consider it Comment from : M Nouman Haider |

|

|

Thank you sir Comment from : Fresh Vlogs |

|

|

the lecture are greatly helpful thanks a lot Comment from : Om Dumbre |

|

|

atishay leend Comment from : CHIRAG AGARWAL |

|

|

ok Comment from : CHIRAG AGARWAL |

|

|

thanks Comment from : Parthiv Shah |

|

|

Won't the flip flop as enabled by the clock at 5:05 be functional only when the clock is high? Like I don't get why is it edge-triggered/edge-sensitive in this particular design Even with a clock, the circuit should remain functional only when the level is high, and not just during transition Am I right?brüôÅüôÅüôÅüôÅ Comment from : Tanmoy Dutta |

|

|

ý§¨ý§πý•Åý§§ ý§Æý§∏ý•çý§§ ý§∏ý§Æý§ùý§æý§§ý•á ý§πý•ã ý§Üý§™ý•§ý•§brý§ßý§®ý•çý§Øý§µý§æý§¶ Comment from : Deepak Kumar |

|

|

A flip flop is composed of two latches This explanation is wrong Changing the enable signal for a clock signal without adding another latch won't change how the circuit works at all Comment from : Santiago Carlos |

|

|

Thank you sir Comment from : Lingaraju Lingaraju |

|

|

Thank you so much sir Comment from : Shylaja S nair |

|

|

wow, excellent Comment from : Educa LK |

|

|

This is really amazingüòç Comment from : Madiya Mirza |

|

|

Thank You Comment from : madushan prathap |

|

|

How to Download This "Multisim" Software Comment from : GameXD |

|

|

I didn't get why its not flip flop in level triggered clock Comment from : Vinayak Bhandage |

|

|

S* is SEn complement right? Comment from : Lovin Babu |

|

|

1 MILLION SUBSCRIBERS COMING SOONüòÅ Comment from : Bhushan Lokhande |

|

|

Thank you so much sir, you are helping a lot by your videos We all are beneficial with your videos brKeep going sir, we all supports you brThank you Comment from : ajay badigineni |

|

|

What is operational and functionsl in given lecture ??? Comment from : CS World |

|

|

If NOR latch used, it will become easier to understand Comment from : Ashish Kumar Burnwal |

|

|

I prefer a latch made with one input of a OR gate as the latch Set input The OR gate output is connected to the input of a AND gate The other input of the AND gate is connected to the output of an inverter The inverter input is the Reset input of the Latch The AND gate output is the Latch output and it is connected to the other input of the OR gate My understanding is that some integrated circuit outputs can not be connected together without measures being taken to prevent damage I call the latch circuit above a reset master since a high reset input always results in a low output To avoid confusion figure any part of the circuit that has a high output is in some way connected to that gates or inverters power supply positive connection To be honest I have not even tested the above circuit but have tested its relay logic equivalent (which is slightly different) Comment from : mark finn |

|

|

?? Comment from : Ali Saba |

|

|

difference between enable and clock ? Comment from : Sanjay kumar Sharma |

|

|

Sir make a clear video on active low and active high enable input Comment from : Saqlain Ahmed |

|

|

I've seen this described better, in a language I could understand Comment from : mr reality |

|

|

At 36 th second of the video diagram for SR latch is wrong , the position of S and R should be reversed But, still you teach really well br! badde log sae choti galtiyan ho jati hae Comment from : Rahul Chauhan |

|

|

Wow you made something so easy--so complicated Comment from : A B |

|

|

Sir please do videos on logic familiesand memories Comment from : Sai nithin Manthena |

|

|

Thank you sir Comment from : Gaurav Gupta |

|

|

PLEASE MAKE VIDEOS ON DIGITAL LOGIC FAMILIES (TTL, ECL, CMOS etc) and ADC and DAC conversionsbrYour lectures are greatbrThank you so much for them Comment from : Pranav Shukla |

|

|

Not clear so good There is only one difference that latch is level sensitive and FF is edge sensitive , it is statement or it has any prove because I was expecting anything more when you added extra NAND gate with the simple Latch Comment from : Arup Ankur |

|

|

S* should be equal to S(bar)x(and)En(bar) Comment from : Shrine |

|

|

Dude, draw gates properly Which are NAND and NOR are not distinguishable from the drawing? Comment from : Mr Junior DEV |

|

|

You told only when enable is high ,it will work as latch but later only when enable is 0 ,we get output as memoryHow is that?Im not clear about itCan anyone explain? Comment from : Naganandhini Kanniappan |

|

|

even a flipflop can be level sensitive Comment from : BoomBeachNoob |

|

|

Thank you! very clear and impressive!! Comment from : Eason Lee |

|

|

Neso is back subscribe Comment from : Abhishek Dubey |

|

|

Im in 2020 Comment from : Rainbow Life |

|

|

Superb Comment from : Govtbankaspirantlife |

|

|

Wow! U r awesome! Please explain Mechanics and Thermodynamics Plss!! Comment from : Kausik Kar |

|

|

this is not a flop flop, because still it is in level sensing mode, Comment from : ahamed Ihthizam |

|

|

So if I set the clock to work as level triggering,will the circuit be call Latch??brBecause latches are level sensitive as you say!!! Comment from : Sankha Suvra Ghatak |

|

|

thanks Comment from : Nevil Holmes |

|

|

very very very niceüëèüëèüëèüëè Comment from : krish vamsi |

|

|

i still dont get what the difference between a latch and a flip flop is someone help!!!!! Comment from : Felix Reyes |

|

|

sir, at 4:43 you said that the circuit will only respond to the edge of the clockbut how does the circuit know that is should respond only at the edge because even in this case the output will change during the high period of the clock pulse Comment from : Dhiraj Kumar Sahu |

|

|

Sir I dont know how to thank u But increadible effort Comment from : Mr L |

|

|

What is title of 121 and 122 lecture? Comment from : Ruturaj Jadhav |

|

|

why we are using NAND gate and formulating the expression with OR operation?? Comment from : Rahul R |

|

|

How to design a low level-sensitive latch using a flip flop? Comment from : Ashmika Singh |

|

|

how output will change in positive edge triggering flipflop when it goes from lower to higher state (0 to 1)brwhy output will not change in positive edge triggering flipflop when it remains in higher state(1)? , as the flipflop will be active when its clock input or enable input is in higher state(1) Comment from : Haroon Khalid |

|

|

invite me when you win the Nobel prize Comment from : Bidaarle |

|

Latch and Flip-Flop Explained | Difference between the Latch and Flip-Flop –Ý—ï–°‚Äö : ALL ABOUT ELECTRONICS Download Full Episodes | The Most Watched videos of all time |

|

Flip Flop In Digital Electronics | Types Of Flip Flops Circuits | Flip Flop In Digital Logic design –Ý—ï–°‚Äö : Pywix Classes Download Full Episodes | The Most Watched videos of all time |

|

Flip Flop in Digital Electronics in Hindi|SR Flip Flop|Zeenat Hasan Academy –Ý—ï–°‚Äö : Zeenat Hasan Academy Download Full Episodes | The Most Watched videos of all time |

|

ÿ¥ÿ±ÿ≠ ŸÇŸÑÿßÿ® SR ÿߟÑÿߟàŸÑ | SR Flip-Flop | Latches and Flip-flops | Set Reset Flip-flops –Ý—ï–°‚Äö : ŸÖŸÜÿ™ÿ∏ÿ± ŸÜÿπŸäŸÖ Muntadher Naeem Download Full Episodes | The Most Watched videos of all time |

|

SR Latch and Gated SR Latch Explained | SR Latch using NOR gates and NAND gates –Ý—ï–°‚Äö : ALL ABOUT ELECTRONICS Download Full Episodes | The Most Watched videos of all time |

|

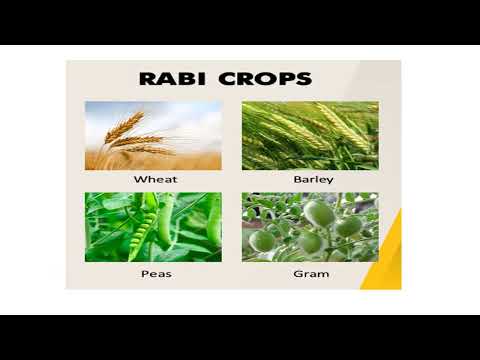

difference between kharif and rabi crops || difference between rabi and kharif crops –Ý—ï–°‚Äö : Janvi Academy Download Full Episodes | The Most Watched videos of all time |

|

ÿ¥ÿ±ÿ≠ ŸÖÿßÿ≥ŸÉ SR ÿߟÑÿߟàŸÑ | SR Latch | Latches and Flip-flops | Set Reset latch –Ý—ï–°‚Äö : ŸÖŸÜÿ™ÿ∏ÿ± ŸÜÿπŸäŸÖ Muntadher Naeem Download Full Episodes | The Most Watched videos of all time |

|

Ep 057: Latch and Flip-Flop Operation –Ý—ï–°‚Äö : Intermation Download Full Episodes | The Most Watched videos of all time |

|

Basic Flip Flop or Latch | Digital Electronics by Raj Kumar Thenua | Hindi / Urdu –Ý—ï–°‚Äö : Learn By Watch Download Full Episodes | The Most Watched videos of all time |